Journal of Nonlinear Analysis and Optimization

Vol. 14, Issue. 1:2023

ISSN: 1906-9685

# DSP APPLICATIONS BASED ROUNDING BASED APPROXIMATE MULTIPLIER FOR HIGH SPEED YET ENERGY EFFICIENT

M Sagar Assistant Professor Department Of ECE Sree Chaitanya College of Engineering,

Karimnagar

K Gouthami Assistant Professor Department Of ECE Sree Chaitanya College of Engineering,

Karimnagar

## Abstract-

This paper proposes a rounding-based approximation multiplier (ROBA) that effectively multiplies two integer integers by shifting them. This study's main objective was to round the number using sign detector results. This work can be implemented using three different hardware functions: a barrel shifter that multiplies the values according to the shifting formula at obtain the approximate value with less delay than various conventional multipliers; a second function for sign sets that indicate exact multiplier, accurate multiplier, and approximate multiplier values based on operands of values a=b, a>b; and a third function for signed multiplication of two integer values. This approximate multiplier with a rounding base can be used in image processing, digital signal processing, and picture sharpening. It is necessary to use the ROBA multiplier.

## **Keywords:**

multipliers, compressors, error tolerance, ROBA, approximation.

#### I. Introduction

The work's objective is to create an approximate multiplier[1] based on rounding by employing shifters. The rounding block is attached to the sign detector. Values that have been rounded should be processed using a shifting operation, a koggee-stone adder and subtract or, assigned, and comparison of the outcomes of the simulation as well as the design and waveforms. Power, latency, space, area, and error rate are estimated for the proposed MAC unit using the ROBA multiplier, and its performance is compared to that of other existing multipliers such the Wallace, Dada, and ROBA multipliers. The suggested MAC unit using the ROBA multiplier offers the best output performance overall, withadelayof3.08ns, 5.3mw of power consumption, and 2.9% relative error rate. In terms of energy [2] intake, approximation techniques in multipliers popularity on accumulation of partial products are crucial. In order to simplify the hardware, a broken array multiplier is implemented, which truncates the least significant bits of inputs when producing partial products. The suggested multiplier in partial product accumulation saves a few adder circuits. In Wallace tree multiplier is very useful hardware function that is used in digital circuit for multiplies two integers. In Wallace method the multiplication of two numbers is done by reducing the partial product matrix into a two- row matrix by a half adder, full adder, carry-save adder and these two rows area fast carry propagate adder to produce the output product. In this Wallace tree method we used half adder for summation of 2 bit and used full adder for summation of 3 bit. For multiplicands of higher than 8 bits this advantage is more beneficial. Because the addition of partial products is low in Wallace tree and hence increase speed. Here each bit of each partial product is every column is added together by a set of counter usedparallel so that is carry is propagated further, then this matrix is reduced[3] by another set of counter until arrow matrix generates. Busing ROBA multiplier to get approximate vale when multiply the two integer values and reduce the error rate, delay, power compared to existing multipliers.

## II. LITRATURE SURVEY

Use of approximation adders in low-power digital signal processing by Raghunathan, and K. Roy was published in IEEE Trans. For portable multimedia devices using a variety of sign processing architectures and algorithms, low strength is a crucial need.

People can often learn something important from results that are just slightly off in most multimedia programmes. We no longercare about offering results that are 100% accurate as a result. Previous research in this field has benefited from errors' resilience through voltage overscaling and used computational and architectural techniques to avoid the following problems. In this paper, [4]a shared experience complexity reduction price at the transistor level is proposed as a feasible method for capacitance's inherent good performance, our solutions produce noticeably shorter critical routes, enabling voltage scalability.

## III.EXISITNG METHOD ROBAMULTIPLIER

A. Hardware Implementation of ROBA Multiplier.

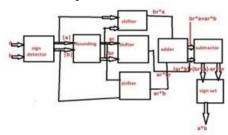

Figure 1:.Block Diagram of ROBA multiplier

The following guidelines should be kept in mind for the unique image of Vd-Orig shown in Fig. 3. Images that have been sharpened using the second method are also included, along with details on the S- ROBA and AS-ROBA multipliers that were used. Figure 3(b)–(d). Figure 3(b)-(d) [5]suggests that the bitterness introduced by the polishing process may not be immediately apparent. Then, at that point, an underlying likeness file metric (MSSIM [20]) is proposed in light of the pinnacle signal-to-commotion proportion (PSNR) of the honed pictures for the two cleaning lattices for seven pictures. It is important to note that the aforementioned PSNRs are calculated just by analysing the captured sharpened picture with the correct multipliers.

It's that time again. Input (output) image pixel located at coordinates (i, j) is represented by (X(i, j)] [Y(i, j) Mask]. For smoothing, a nn matrix of coefficients is supplied by.

$$Mask_{smoothing} = \begin{bmatrix} 1 & 1 & 1 & 1 & 1 \\ 1 & 4 & 4 & 4 & 4 \\ 1 & 4 & 12 & 4 & 7 \\ 1 & 4 & 4 & 4 & 4 \\ 1 & 1 & 1 & 1 & 1 \end{bmatrix}.......(5.6)$$

Since each coefficient is strong, each of the three ROBA multiplier topologies generates output pictures of high quality. For the seven photos being evaluated using the noteworthy multiplier,[6] Table IX shows the PSNR and MSSIM of the smoothing technique utilizing the recently referenced derived multiplier systems. The discoveries show that all PSNRs (MSSIMs) are higher than 40 (0. 989), indicating a slight error in the suggested multiplier. The ROBA's output is superior to that of the DRUM6 and Mitchell multipliers in every benchmark image. The DSM8 multiplier, on the other hand, offers the great outcome superb, exactly as the beautification software.

## IV. PROPOSED METHOD RESULTS

A. RTL Schematic of ROBA Multiplier

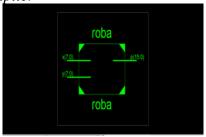

Figure 2:RTL Schematic of ROBA Multiplier is 8 bit

In figure shown above ROBA Multiplier is 8bit data it multiply the 8 bit for two integer values to get 16bit data.

A. Technology View Of The ROBA Multiplier:

As per shown above contains the blocks are sign detector, rounding, shifters, koggestoneadder, subtractor, sign set.

Figure 3:Technology View Of the ROBA Multiplier

B. Simulation Result of Signed Multiplication For ROBA Multiplier:

Figure 4: Simulation Result Of signed For ROBA Multiplier

Calculation:

Roba for signed multiplication

A=-35; B=47 Rounded Ar=36; rounded Br=47 Mathematical operation of roba multiplier is given by A\*B=(Ar\*B)+(Br\*A)-(Ar\*Br) aftershifting operationThen (36\*47)=(36\*47)+(47\*-35)-(36\*47)1645=1645

C. Simulation Result of Unsigned Multiplication for ROBA Multiplier:

Figure 5:Simulation Result Signed Multiplication for ROBA Multiplier

D. Roba for unsigned calculation:

A=86; B=27Rounded Ar=64; rounded Br=27 Mathematical operation of roba multiplier is given by \*B=(Ar\*B)+(Br\*A)-(Ar\*Br) after shifting operation Then (86\*27)=(64\*27)+(27\*86)-(64\*27)2322=2322

E. Timing Report Analysis of ROBA Multiplier:

Figure 6:Timing Report Analysis of ROBA Multiplier To get the result with less delay for 5.223ns by performing ROBAmultiplier

F. Power Report Analysis of ROBA Multiplier:

Figure 7:Power Report Analysis Of RobaPower report for roba multiplier is 324.78mw .Inuput

output thermal power dissipation is 21.80mw.

G. Aging Aware Multiplier Output of Schematic View 16\*16 Wallace TreeMultiplier

Figure 8: Normal 16x16 Multiplier Schematic Diagram

The inputs are aging aware multiplier is 16 bit and get the 16 bit data output with respect gating, multiplexer, aging indicater blocks to be performed.

H. Simulation Result of Wallace Tree Multiplier Using Aging Aware Multiplier:

Figure 9:Simulation Result Of Wallace Tree Multiplier 16\*16 using Aging AwareMultiplier

I. Schematic View of The Column Multiplier:

Figure 10:Schematic View Of The Column Multiplier

A multiplier that skips across four columns. Assuming the inputs are 10102 \* 11112, we can see that the supply bit from the top-right FA and the partial product aibi are both zero for the FAs in the first and 1/three diagonals. As a result, the sum bit at the output of the adders is equivalent to zero since the output occurs on all diagonals. Its true output is the sum of its upper FA's 33 bits.

J. Simulation Result of Colum Multiplier:

Figure 11:Simulation Result of Colum Multiplier

Schematic View of Row Multiplier:

Figure 12:Schematic View Of Row Multiplier 16\*1

A four4 row-bypassing multiplier is shown in figure three. Each doorway leads to an FA through a tristate gate. The two inputs within the first and second rows are both 0 for FAs when the inputsare 11112 \* 10012. The first row of multiplexers choose aib0 [7] because the sum bit is 1, and it selects out 0 because the deliver bit is 1. This is because b1 is 0. Bypassing their inputs and blocking their entry pathways, 2d-row FAs are circumvented using tri-state gates.

K. Simulation Result of Row Multiplier:

| *                                          |           |                            | 3,000.000 no      |

|--------------------------------------------|-----------|----------------------------|-------------------|

| Name                                       | Value     | 2,200 ns 2,400 ns 2,600 ns | 2,800 ns 3,000 ns |

| ■ M a(30)                                  | 0100      | 8100                       |                   |

| ▶ ₩ b(3d)                                  | 0010      | 0010                       |                   |

| ▶ ¾ p(7d)                                  | 00002000  | 00001000                   |                   |

| <ul> <li>* ** ** ** ** ** ** **</li> </ul> | 10        | 10                         |                   |

| 🗠 > 🐕 entra es                             | 000000000 | 000000000000               |                   |

| tr lie pt                                  | 0         |                            |                   |

| lie p2                                     | 0         |                            |                   |

| le pl                                      | 0         |                            |                   |

| liè pi                                     | 0         |                            |                   |

| le ps                                      | 0         |                            |                   |

| ùaipt<br>ùaips<br>⊟ ùaips                  | :         |                            |                   |

| 10.0                                       | _         |                            |                   |

Figure 13: Simulation Result of Row Multiplier

## V. CONCLUSION

In this work, the ROBA multiplier—a green approximation multiplier with high speed and potency—was proposed. The highly accurate multiplier that was suggested was based on the supposition that the inputs are rounded to a2n-shaped values. By ignoring the computationally important region of multiplications, speed and energy consumption were increased at the expense of a few minor errors. The proposed approach can now be used to effectively do multiplications, both signed and unsigned. Three distinct hardware implementations of the approximation multiplier were intended, one for each signed and unsigned operation.

## A. FUTURE SCOPE

Using a shifting operation to multiply two integer numbers and obtain an approximate result in less time is known as a rounding-based approximate multiplier. If processing a greater amount, we use nested ROBA or an approximation multiplier based on adjusted rounding to obtain the precise value.

## REFERENCES

- [1]. Reza Zendegani, Mehdi Kamal, Milad Bahadori, Ali Afzali- Kusha and Massoud Pedram," RoBA Multiplier: A Rounding-Based Accurate Multiplier for High-Speed yet Energy EnergyEfficient Digital Signal Processing" IEEE transactions on very large scale integration (VLSI) systems syst., pp.1-9, July 2017.

- [2]. K. Bhardwaj and P. S. Mane, "ACMA: Accuracy-configurable multiplier architecture for errorresilient system-on-chip," in Proc. 8th Int. Workshop Reconfigurable Commun.- Centric Syst.-Chip, 2013, pp.1–6.

- [3]. S. Narayanamoorthy, H. A. Moghaddam, Z. Liu, T. Park, and N. S. Kim, "Energy-efficient accurate multiplication for digital signal processing and classification applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

- [4]. D. R. Kelly, B. J. Phillips, and S. Al-Sarawi, "Accurate signed binary integer multipliers for arithmetic data value speculation," in Proc. Conf. Design Archit. Signal Image Process., 2009, pp. 97–10.

- [5]. A.B. Kahng and S.Kang,"Accuracy-configurable adder for accurate arithmetic designs," in Proc 49th Design Autom Conf (DAC), Jun 2012, pp.820-825.

- [6]. S. Deepak, B J kaliath,"Optimized MAC unit Design". Electron devices and solid state circuit IEEE international conference on 2012.

- [7]. P. Siva Nagendra Reddy and M. Saraswathi," Design and Implementation of FPGA based 64-bit MAC Unit using VEDIC Multiplier and Reversible Logic Gates, Indian Journal of Science and Technology, Vol10(3), DOI:10.17 485/ijst/2017/v10i3/109413, January 2017.

- [8] S. Deepak, B J kaliath,"Optimized MAC unitDesign". Electron devices and solid state circuit IEEEinternational conference on 2012.